# Circuits Numériques

#### **CHAPITRE 7:**

Les bascules (latch et flip-flop)

#### A la fin de ce chapitre, vous devez être capable:

- D'expliquer et de retrouver la table de vérité des principales bascules synchrones et asynchrones (RS, D, JK ..)

- D'expliquer le principe du maître-esclave

- De définir et d'utiliser les spécifications dynamiques des bascules (temps de propagation, de setup, de hold, fmax ...)

#### Sommaire

- 1. Définitions

- 2. Les bascules asynchrones

- 3. Les bascules synchrones actives sur état

- 4. Les bascules synchrones actives sur front

- 5. Caractéristiques dynamiques des bascules

- 6. Synthèse

#### 1. Définitions

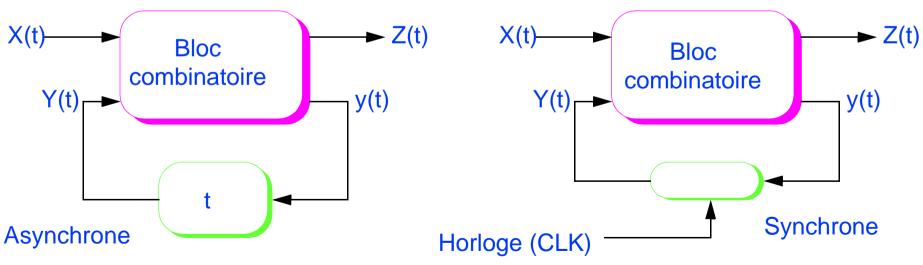

- Logique séquentielle

La combinaison des sorties ne dépend pas seulement de celle des entrées mais aussi de l'état précédent des sorties.

- Types de circuits

Astable: le circuit ne possède pas d'état stable (oscillateur)

Monostable: le circuit possède un état stable et un état fugitif de durée déterminée déclenché par un évènement particulier (trigger)

Bistable: le circuit possède deux états stables (mémoire)

- Circuits synchrones et asynchrones

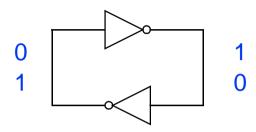

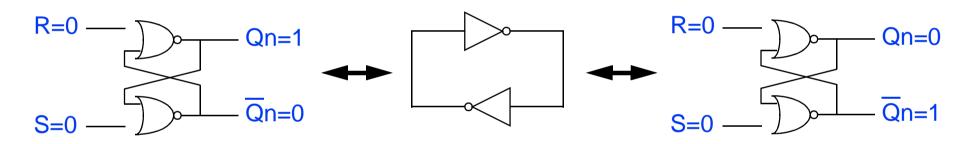

#### Circuit minimal

Bascule: circuit bistable

il faut un moyen de fixer l'état désiré

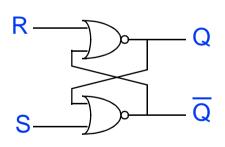

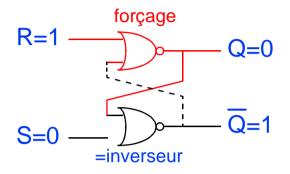

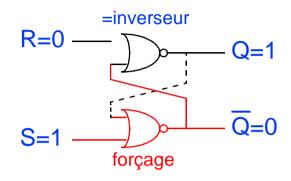

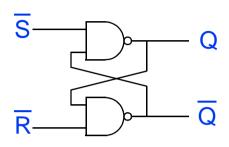

#### La bascule RS

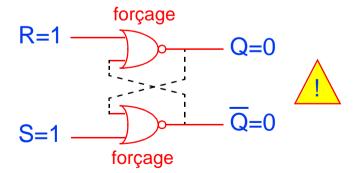

|   | R | S | Qn   | Qn   |                         |

|---|---|---|------|------|-------------------------|

| - | 1 | 0 | 0    | 1    |                         |

| - | 0 | 1 | 1    | 0    |                         |

| - | 0 | 0 | Qn-1 | Qn-1 | état mémoire            |

|   |   |   | 3    | 0    | combinaisor indésirable |

S (SET): mise à 1 R (RESET): mise à 0

#### La bascule RS

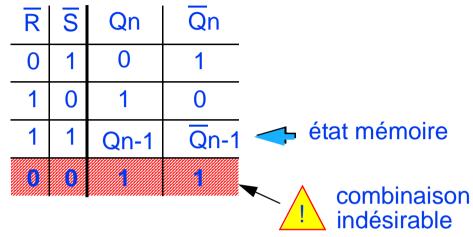

Application de la bascule RS: circuit anti-rebonds

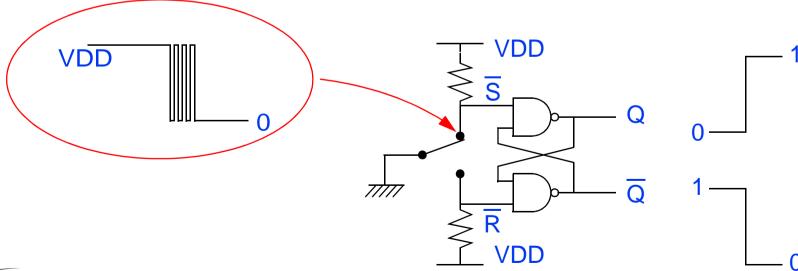

La bascule JK

| 0 1 0 1                      | J | K | Qn   |                             |

|------------------------------|---|---|------|-----------------------------|

| o o QII-I QII-I              | 0 | 1 | 0    |                             |

| o o QII-I QII-I              | 1 | 0 | 1    | 0                           |

| 1 1 Qn-1 Qn-1 ← état mémoire | 0 | 0 | Qn-1 | Qn-1 ← état mémoire         |

|                              | 1 | 1 | Qn-1 | Qn-1 <del>tat mémoire</del> |

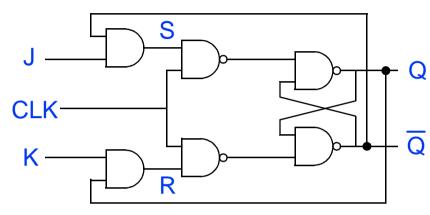

$Qn+1 = J \overline{Q}n + \overline{K} Qn$

- Limitations des bascules asynchrones

- Fonctionnement asynchrone: la sortie réagit "immédiatement" à l'entrée

- Les entrées doivent donc rester stables

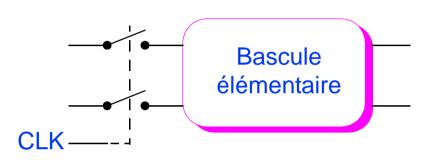

#### Principe

CLK inactif: la bascule est isolée (il faut s'assurer qu'elle se trouve en configuration mémoire)

CLK actif: la bascule fonctionne normalement

Rmq: "actif" ne signifie pas nécessairement au niveau haut (1)

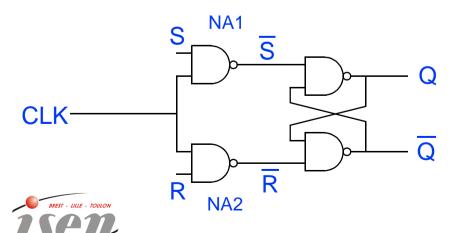

Bloc de base: la bascule RS synchrone

CLK = 0, R et S indifférents car NA1 et NA2 imposent un état  $\overline{R} = \overline{S} = 1$  et par conséquent:

CLK = 1: fonctionnement classique de la bascule car NA1 et NA2 se comportent en inverseurs

la bascule est transparente: la sortie réagit "immédiatement" à l'entrée lorsque CLK=1

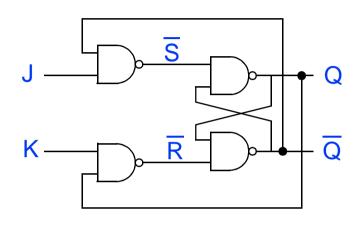

#### La bascule JK synchrone

CLK = 0, J et K indifférents : Qn = Qn-1 (état mémoire)

CLK = 1: fonctionnement classique de la bascule

CLK = 1: la bascule est transparente

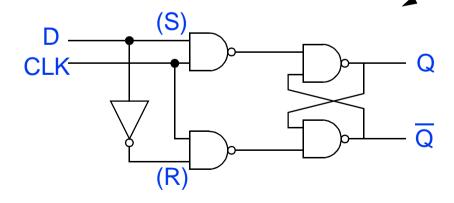

La bascule D synchrone

| D | CLK | Qn   |

|---|-----|------|

| X | 0   | Qn-1 |

| 1 | 1   | 1    |

| 0 | 1   | 0    |

D (Data) = donnée

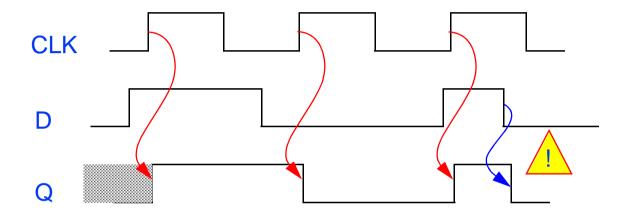

Inconvénient des bascules synchrones actives sur état (exemple de la bascule D)

- La transition en sortie semble déclenchée par un front d'horloge

- La sortie peut évoluer pendant le temps où CLK = 1

- les entrées doivent rester stables lorsque CLK = 1

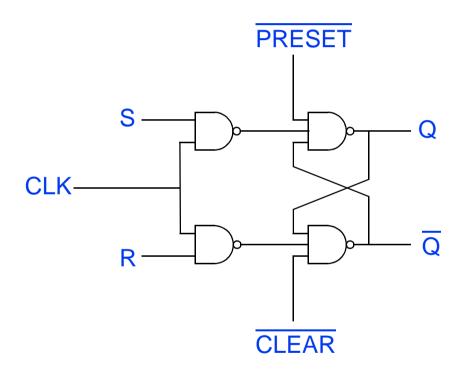

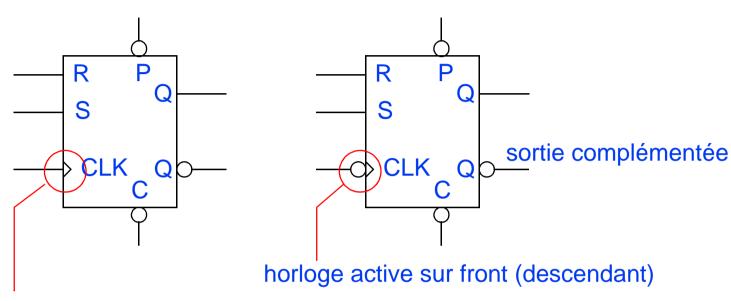

#### Entrées d'initialisation

exemple de la bascule RS

$$\overline{\text{PRESET}} = 0$$

,  $\overline{\text{CLEAR}} = 1 \longrightarrow Q = 1$

$$\overline{\mathsf{PRESET}} = 1, \overline{\mathsf{CLEAR}} = 0 \longrightarrow \mathsf{Q} = 0$$

Les entrées d'initialisation sont asynchrones

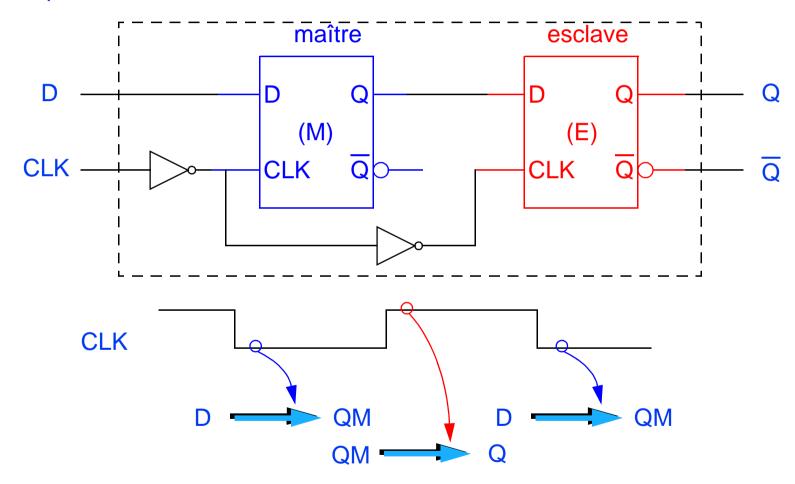

Bascules maître-esclave (exemple de la bascule D)

Principe: maître et esclave travaillent en alternance

Elimine la nécessité d'avoir des entrées stables lorsque CLK est actif Dans cet exemple, la donnée apparaît en Q (et  $\overline{Q}$ ) lors du front montant de CLK

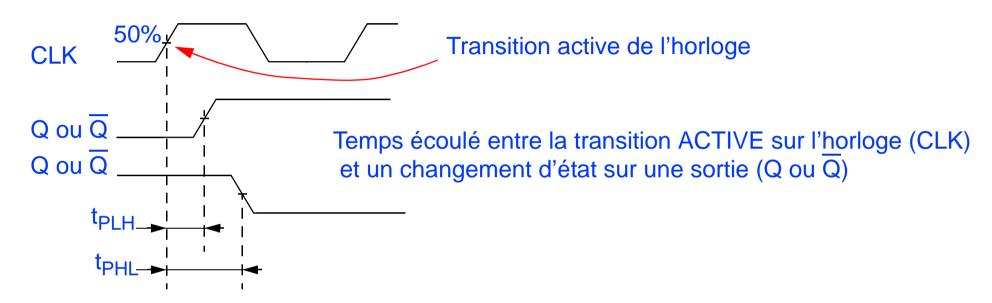

# 5. Caractéristiques temporelles des bascules

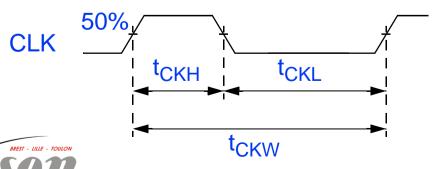

Temps de propagation

Durée d'impulsion (pulse duration)

t<sub>CKL</sub> et t<sub>CKH</sub> doivent permettre aux bascules maître et esclave de se positionner correctement

$$t_{ckw} = \frac{1}{f_{max}}$$

### 5. Caractéristiques temporelles des bascules

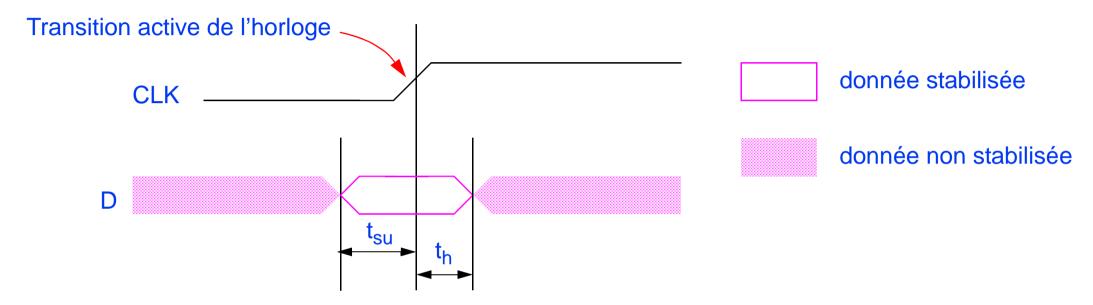

Temps de prépositionnement (setup time, t<sub>su</sub>) et de maintien (hold time, t<sub>h</sub>)

t<sub>su</sub> et t<sub>h</sub> permettent à la bascule maître d'effectuer sa transition vers un état mémoire avec des données d'entrée stables

t<sub>su</sub> et t<sub>h</sub> ne sont pas nécessairement égaux, t<sub>h</sub> peut être nul

La transition active de l'horloge <u>n'est pas obligatoirement</u> un front montant

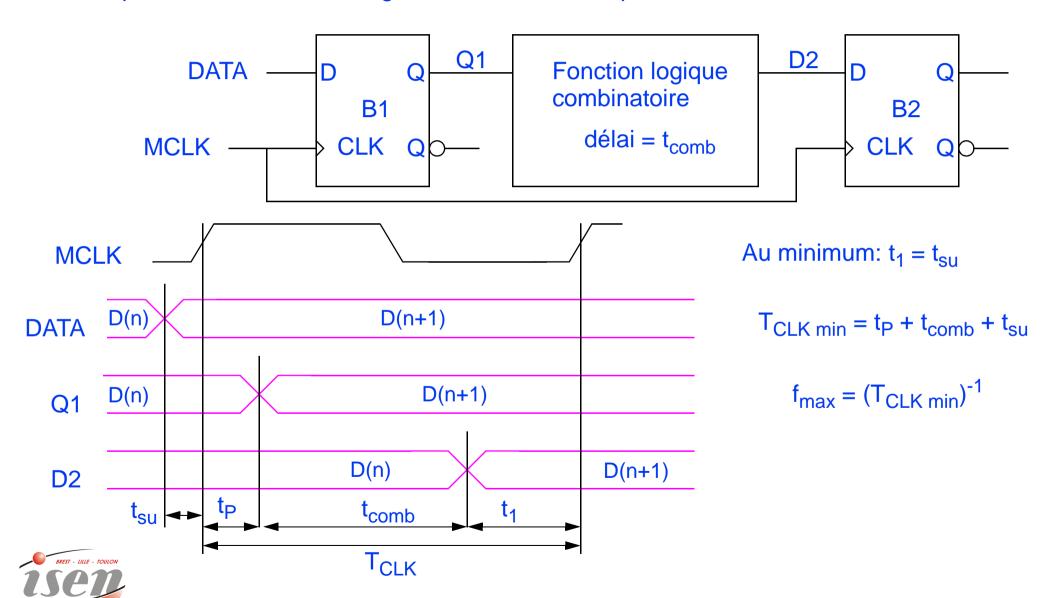

### 5. Caractéristiques temporelles des bascules

Fréquence maximale d'horloge dans un circuit comportant des bascules

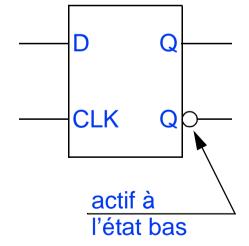

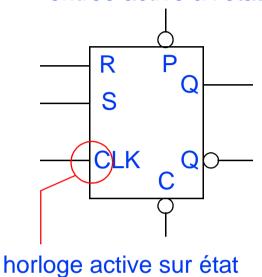

### 6. Synthèse

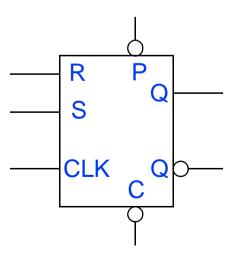

entrée active à l'état bas

horloge active sur front (montant)

Bascule avec horloge active sur état = latch (verrou)

Bascule avec horloge active sur front = Flip-Flop

Dans une bascule, il n'y a <u>pas de relation temporelle directe</u> entre les entrées (R, S, J, K ou D) et la sortie Q. Les temps caractéristiques <u>sont définis par rapport à l'horloge</u> CLK:

$t_{su}$ ,  $t_h$  entre CLK et les entrées de données (R S, J, K ou D)  $t_P$  entre CLK et les sorties Q et  $\overline{Q}$